# Real Coded Genetic Algorithm Approach to Harmonic Reduction in Multilevel Inverters for Drives

Adeyemo, I. A.<sup>1</sup>, Fakolujo, O. A.<sup>2</sup>., Aborisade, D. O.<sup>3</sup>

<sup>1, 3</sup>Electronic & Electrical Engineering Dept.

<sup>2</sup>Electrical & Electronic Engineering Dept.

<sup>1, 3</sup>Ladoke Akintola University of Technology, PMB 4000, Ogbomoso, Oyo State, Nigeria.

<sup>2</sup>University of Ibadan, Ibadan, Oyo State, Nigeria.

Correspondence: iaadeyemo@lautech.edu.ng, ao.fakolujo@ui.edu.ng, doaborisade@lautech.edu.ng

**Abstract** – Unlike utility application that requires a constant-frequency, constant-voltage high power multilevel inverter, adjustable speed drives (ASDs) used to control large industrial motors require high power variable-frequency and variable-voltage multilevel inverters that can operate over a wide range of modulation indices. In this paper, Real Coded Genetic Algorithm (RCGA) is proposed for computing the switching angles required to eliminate low order harmonics up to 13th order from multilevel inverter voltage waveform while keeping the magnitude of the fundamental at the desired level. RCGA is simple, derivative free, and globally convergent with any random initial values. The global search capability of RCGA is demonstrated in its ability to find solutions in the regions that are infeasible for other existing methods to find solutions. Both analytical and simulation results show that the proposed method efficiently mitigates harmonic distortion in multilevel inverter.

Keywords- Multilevel inverter, Selective Harmonics Elimination (SHE), Real Coded Genetic Algorithm (RCGA), drives

# I. INTRODUCTION

Sequel to the advances made in power electronic conversion and control system over years, adjustable speed drives (ASDs) are increasingly used in place of mechanical gears for variable speed control applications in industries. High-power induction motor drives using classical twolevel ASDs suffer from poor voltage and current qualities. The conventional two-level inverter's high voltage change rates induce circulating currents, dielectric stresses, voltage surge, and corona discharge between the winding layers, which cause "motor bearing breakdown" and motor winding insulator breakdown" problems [1]. These problems become more significant as the switching speed of power semiconductor devices increases.

Multilevel power conversion is a rapidly growing area of power electronics with good potential for further development. The concept of utilizing multiple small voltage steps to perform power conversion was developed from the idea of step approximation of sinusoid [2]. The unique structure of multilevel converters enables the construction of relatively high power converters with improved harmonic spectrum using relatively low power semiconductor devices. This has resulted into the ability of the converters to meet stringent power quality and high power demands. There are several advantages to multilevel power conversion approach when compared with the traditional two-level power conversion. The smaller voltage steps yield lower switching losses, improved power quality, lower electro-magnetic interference (EMI), lower voltage change rate (dv/dt), and lower torque ripple [3], [4].

Several topologies and control algorithms of multilevel inverter have been reported in literature. However, the three main topologies are diode-clamped inverter which is based on neutral point converter [5], flying capacitor inverter [6], and Cascaded H-bridge inverter [7]. Due to the versatility of multilevel converter, various modulation techniques such as Sinusoidal Pulse Width Modulation (SPWM), Selective Harmonic Elimination (SHE) method, Space Vector Control (SVC), and Space Vector Pulse Width Modulation (SVPWM) [3], [4] that are used in conventional two-level inverter have been modified and deployed in multilevel converters.

Unlike utility application that is a constant frequency, high power application, large industrial motors are controlled using high power variable-frequency and variable-voltage drives. Consequently, utility requires only one solution set at a particular modulation index while adjustable speed drives (ASD) need multiple solution sets over a wide range of modulation indices. For drives application, selective harmonic elimination-pulse width modulation (SHE-PWM) multilevel inverter switching at fundamental frequency arguably gives the best spectral performance. The main challenge associated with SHE method is how to obtain analytical solutions of the nonlinear transcendental equations that contain trigonometric terms [8].

Several methods that have been reported for solving SHE equations can be classified into two groups: The first group is based on deterministic approach using exact algorithms. Newton Raphson iterative method [9] is one of these. The main disadvantage of iterative methods is that they diverge if the arbitrarily chosen initial values are not sufficiently close to the roots. They also risk being trapped at local optima and fail to give all the possible solution sets. The theory of symmetric polynomials and resultants [10] has been proposed to determine the solutions of the SHE equations. A difficulty with this approach is that as the number of levels increases, the order of the polynomials becomes very high, thereby making the computations of solutions of these polynomial equations very complex. Another approach uses Walsh functions [11], [12], [13] where solving linear equations, instead of non-linear transcendental equations, optimizes the switching angle. The method results in a set of algebraic matrix equations and the calculation of the optimal switching angles is a complex and time-consuming operation.

The second group is based on probabilistic approach using evolutionary algorithms that minimize rather than eliminate the selected harmonics. Evolutionary algorithms such as genetic algorithm [14], [15] particle swarm optimization [16], ant colony system [17], bee algorithm [18] etc are derivative free and are successful in locating the optimal solution, but they are suffer from excessive utilization of computing resources specifically time and memory.

# **II.** MULTILEVEL INVERTER

#### A. Multilevel Inverter Topologies

The core enabling technology in ASDs is the power conversion technique. While multilevel converter deals with both AC-DC and DC-AC conversions, multilevel inverter deals solely with DC-AC conversion. Diode-clamped multilevel converter connected back-toback is the ideal where an AC source is the only convenient power source. However, for high voltage and high power quality applications, cascaded multilevel inverter with separate DC sources is more suitable because of its modular structure and circuit layout flexibility.

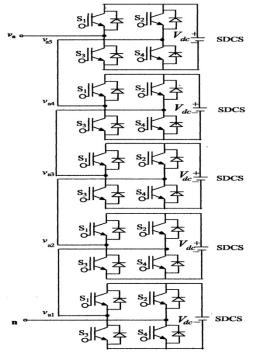

Cascaded H-bridge multilevel inverter is formed by connecting several single-phase H-bridge inverters in series as shown in Fig.1 for an 11-level inverter. The number of output voltage levels in a cascaded H-Bridge inverter is given by N=2S+1, where s is the number of Hbridges per phase connected in cascade. By different combinations of the four switches  $S_1$ ,  $S_2$ ,  $S_3$ , and  $S_4$ shown in the Fig.1, each H-bridge switch can generate a square wave voltage waveform on the AC side.

Fig. 1. Single-phase structure of an 11-level cascaded H-bridge multilevel converter

To obtain  $+V_{dc}$ , switches  $S_1$  and  $S_4$  are turned on, whereas  $-V_{dc}$  can be obtained by turning on switches  $S_2$  and  $S_3$ . By turning on  $S_1$  and  $S_2$ , or  $S_3$  and  $S_4$ , the output voltage is zero. The outputs of H-bridge switches are connected in series such that the synthesized AC voltage waveform is the summation of all voltages from the cascaded H-bridge cells [10].

## B. Selective Harmonic Elimination PWM

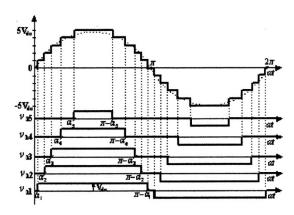

The number of output phase voltage levels in a cascaded H-Bridge inverter is given by N = 2S + 1, where S is the number H-bridges per phase connected in cascade. Assuming a quarter wave symmetry and equal amplitude of the DC voltages, Fourier series expansion of the staircase output voltage waveform shown in Figure 2 is given by equation (1).

$$V(\omega t) = V_n(\alpha) \sin(n\omega t) \tag{1}$$

Where

$$V_n(\alpha) = \frac{4V_{dc}}{n\pi} \sum_{k=1}^{s} \cos(n\alpha_k) \text{, for odd n}$$

(2)

$$V_n(\alpha) = 0$$

, for even n (3)

Fig. 2. Output voltage waveform of an 11-level cascaded H-bridge multilevel converter using fundamental frequency switching scheme.

In three-phase power system, the triplen harmonics in each phase need not be cancelled as they automatically cancel in the line-to-line voltages as a result only non-triplen odd harmonics are present in the line-toline voltages [10]. From Eqns. (1), (2) and (3),

$$v(\omega t) = \sum_{n=1,3,5\dots}^{\infty} \frac{4V_{dc}}{n\pi} (\cos(n\alpha_1) + \cos(n\alpha_2) + \dots$$

(4)

$+\cos(n\alpha_s))\sin n\omega t$

Subject to  $0 < \alpha_1 < \alpha_2 < ... \alpha_s \le \pi/2$

Generally for *s* number of switching angles, one switching angle is used for the desired fundamental output voltage  $V_1$  and the remaining (*S*-1) switching angles are used to eliminate certain low order harmonics that dominate the Total Harmonic Distortion (THD) such that equation (4) becomes

$$V(\omega t) = V_1 \sin(\omega t) \tag{5}$$

From equation (4), the expression for the fundamental output voltage  $V_1$  in terms of the switching angles is given by

$$V_1 = \frac{4V_{dc}}{\pi} \left( \cos(\alpha_1) + \cos(\alpha_2) + \dots + \cos(\alpha_s) \right)$$

(6)

The relation between the fundamental voltage and the maximum obtainable fundamental voltage  $V_{1max}$  is given by modulation index. The modulation index,  $m_i$ , is defined as the ratio of the fundamental output voltage  $V_1$  to the maximum obtainable fundamental voltage  $V_{1max}$ . The maximum fundamental voltage is obtained when all the switching angles are zero [9]. From equation (6),

$$V_{1\max} = \frac{4SV_{dc}}{\pi} \tag{7}$$

$$\therefore m_i = \frac{V_1}{V_{1 \max}} = \frac{\pi V_1}{4SV_{dc}}$$

Consequently,

$$V_1 = m_i \left(\frac{4SV_{dc}}{\pi}\right) \quad \text{for } 0 < m_i \le 1$$

(8)

To develop an 11-level cascaded multilevel inverter, five SDCSs are required. The modulation index and switching angles that result in the synthesis of AC waveform with the least Total Harmonic Distortion (THD) can be found by solving the following nonlinear and transcendental equations characterizing the harmonics derived from equations (1), (2) and (4).

$$\frac{4V_{dc}}{\pi} (\cos(\alpha_1) + \cos(\alpha_2) + ... + \cos(\alpha_5)) = V_1$$

$$\cos(5\alpha_1) + \cos(5\alpha_2) + ... + \cos(5\alpha_5) = V_5$$

$$\cos(7\alpha_1) + \cos(7\alpha_2) + ... + \cos(7\alpha_5) = V_7$$

$$\cos(11\alpha_1) + \cos(11\alpha_2) + ... + \cos(11\alpha_5) = V_{11}$$

$$\cos(13\alpha_1) + \cos(13\alpha_2) + \dots + \cos(13\alpha_5) = V_{13}$$

(9)

In eqn. (9),  $V_5$ ,  $V_7$ ,  $V_{11}$ , and  $V_{13}$  are set to zero to in order to eliminate 5<sup>th</sup>, 7<sup>th</sup>, 11<sup>th</sup> and 13<sup>th</sup> harmonics respectively. The correct solution must satisfy the condition

$$0 \le \alpha_1 < \alpha_2 < \dots < \alpha_5 \le \frac{\pi}{2}$$

(10)

Equation (8) in equation (9) yields:

$$\cos(\alpha_{1}) + \cos(\alpha_{2}) + ... + \cos(\alpha_{5}) = 5m_{i}$$

$$\cos(5\alpha_{1}) + \cos(5\alpha_{2}) + ... + \cos(5\alpha_{5}) = 0$$

$$\cos(7\alpha_{1}) + \cos(7\alpha_{2}) + ... + \cos(7\alpha_{5}) = 0$$

$$\cos(11\alpha_{1}) + \cos(11\alpha_{2}) + ... + \cos(11\alpha_{5}) = 0$$

$$\cos(13\alpha_{1}) + \cos(13\alpha_{2}) + ... + \cos(13\alpha_{5}) = 0$$

(11)

Generally equation (11) can be written as

$$F(\alpha) = B(m_i) \tag{12}$$

The Total Harmonic Distortion (THD) is computed as shown in equation (13):

$$THD = \sqrt{\sum_{i=5,7,11,13,...}^{49} \left(\frac{V_i}{V_1}\right)^2}$$

(13)

# III. REAL CODED GENETIC ALGORITHM

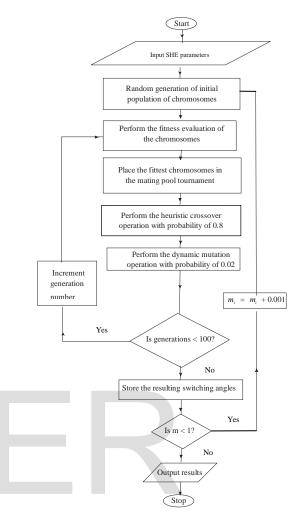

Genetic Algorithm (GA) proposed by Holland in 1975 is a stochastic algorithm that is based on natural evolution [19]. He proposed a Binary-Coded Genetic Algorithm (BCGA) modeled on Darwinian principles of survival of the fittest, with a random but structured exchange of information. Over successive generations, the parameters of a randomly created initial population of individuals, or potential solutions to the problem called strings or chromosomes are repeatedly modified by GA to create new (and hopefully better) population of solutions. This process is repeated for a number of generations until the desired solution is obtained as shown in the flowchart in Fig. 3.

Generally, GA uses three procedures to create the next generation from the current generation. The procedures are:

**Selection:** GA begins the creation of new generation with the selection of chromosomes from the parent population based on their fitness evaluation. The fitness function is the function that is responsible for the evaluation of the solutions at each step.

**Crossover:** Crossover operator is the main genetic operator, and it is applied with certain probability. Chromosome parts of selected parents are swapped to form new offsprings for the next generation.

**Mutation:** In order to introduce diversity and prevent premature convergence, the genetic properties of the new offsprings are deliberately altered with a low mutation probability.

The process of selection, crossover, and mutation is repeated until a maximum number of generations is reached or until the objective function has reached a preset value. The choice of genetic operators is a tradeoff between accuracy and speed, which means that an increase in the accuracy of a solution can only come at the expense of the convergent speed and vice versa. To improve the convergent speed of BCGA, Real-Coded Genetic Algorithms (RCGA) was introduced. For real valued numerical optimization problems, floating point representation outperform binary representation. The main advantages of RCGA are improved accuracy and enhanced convergent speed resulting from a reduced computational effort (BCGA uses binary code, which involves coding and decoding of the parameters) [20].

Fig.3. Flowchart of RCGA for SHE problem

# IV. IMPLEMENTATION

In this work, the population size is 40. The genetic operators are tournament selection, heuristic crossover at the rate of 0.8, and dynamic or non-uniform mutation at the rate of 0.02. In an 11-level inverter, there are five switching angles which translate into five genes in a chromosome. Each chromosome (potential solution) of the transcendental nonlinear equations is encoded as a real value numbers of the same length as the dimension of the search space. For each chromosome (potential solution), the fitness function is calculated as follows [21]:

$$f = \min_{\alpha_i} \left[ \left( 100 \frac{V_1^* - V_1}{V_1^*} \right)^4 + \sum_{s=2}^5 \frac{1}{h_s} \left( 50 \frac{V_{hs}}{V_1} \right)^2 \right] \quad (14)$$

$$i = 1, 2 \dots 5$$

Subject to  $0 \le \alpha_1 < \alpha_2 \dots < \alpha_5 \le \frac{\pi}{2}$

Where  $V_1^*$  is the desired fundamental output voltage, S is the number of switching angles and  $h_s$  is the order of the *s*<sup>th</sup> viable harmonic at the output of a three phase multilevel converter. For example,  $h_2 = 5$ ,  $h_4 = 11$ . The objective here is to determine the optimal switching angles such that the selected harmonics are either eliminated or minimized. It should be noted that different weight are assigned to different harmonics. The fitness function assigns Eqn. (14) assigns higher importance to the low order harmonics, which are more harmful and difficulty to remove with filter.

The RCGA code for each state is run twice, because it may fall into local minima. The least fitness function between both runs is chosen. By increasing the number of runs, the probability of reaching the global minimum increases but the convergent speed decreases due to the increase in the execution time. Also, the default number of generations is 100 but sometimes, RCGA converges to a solution much before 100 generations are completed. In order to save time, generations are halted if the result remains unchanged for 50 generations.

A personal computer (2.66 GHz Intel Core i7 processor with 4GB Random Access Memory) running MATLAB R2014b on OS X Yosemite version 10.10 was used to carry out the computations. The solutions were computed by incrementing the modulation index,  $m_i$  in steps of 0.001 from 0 to 1. For values of the fitness function less or equal to 0.01, SHE equations are solvable, otherwise they are unsolvable.

In order to validate the observed analytical results, an 11-level single-phase Cascaded H-Bridge inverter was modelled in MATLAB-SIMULINK environment using SimPower system block set. In each of the five H-Bridges in the 11-level single-phase Cascaded H-Bridge inverter, 12V dc source is the SDCS, and the switching device used is Insulated Gate Bipolar Transistor (IGBT). Fundamental frequency switching scheme was adopted in this work because of its simplicity and low switching losses. Simulations were performed for different modulation indices using solution sets previously calculated offline with RCGA algorithm. The corresponding THD value of each solution set was measured using the FFT block.

#### V. RESULTS

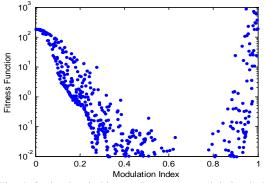

For an 11-level inverter, the plot of fitness value for each set of switching angles versus modulation indices over the range of 0.1 to 1.0 is shown in Fig. 4. For some modulation indices, no solution sets are found. For those modulation indices, it is either there is no solution set or RCGA could not find one. The former reason is more plausible than the latter. At low modulation indices [0, 0.262] as well as at high modulation indices [0.929, 1], the resulting fitness function value is high, hence no solutions are obtained, and the low order harmonics are neither minimized nor eliminated.

Fig. 4. Optimal switching angles versus modulation index

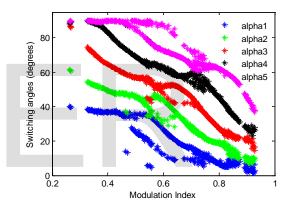

The plot of the switching angles that minimize the  $5^{th}$ ,  $7^{th}$ ,  $11^{th}$  and  $13^{th}$  harmonics for values of modulation indices ranging from 0 to 1.0 is shown in Fig. 5. As the plot in Fig, 5 shows, there are multiple solution sets at some modulation indices. In such cases, the solution set with the least THD value is chosen.

Fig. 5. Switching angles in degree versus modulation index

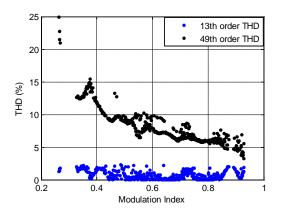

The plots of 13<sup>th</sup> order and 49<sup>th</sup> order Total Harmonic Distortion (THD) versus modulation index are shown in Fig. 6. From the plots, it is observed that in the regions where exact solutions exist, the selected low order harmonics are eliminated while they are considerably minimized in the regions that are not feasible to find exact solutions. However, for all values of modulation index that solutions are found, the maximum 13<sup>th</sup> order harmonic is 2.35%.

Fig. 6 THDs versus modulation index

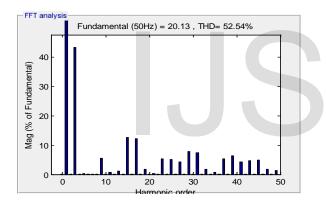

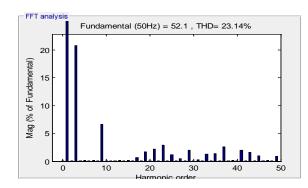

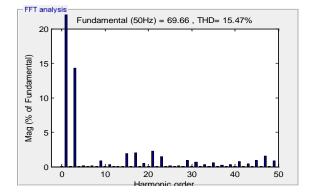

The FFT analysis of the synthesized output voltage of the simulated 11-level inverter at the arbitrarily chosen modulation indices of 0.265, 0.682, and 0.912 are shown in Figures 7, 8, and 9, respectively. From the figures, it is apparent that RCGA has been successful in considerably minimizing the selected harmonics as their values tend towards zero.

Fig. 7 FFT analysis of an 11-level inverter at  $m_i = 0.265$

Fig. 8 FFT analysis of an 11-level inverter at  $m_i = 0.682$

Fig. 9 FFT analysis of an 11-level inverter at  $m_i = 0.912$

The comparative analysis of the analytical and simulation values of the fundamental output voltage at different modulation indices is shown in Table I. It can be seen from the table that the analytical and simulation values of the fundamental output voltage are in close agreement thereby validating the analytical results.

TABLE I: Analytical and simulation values of the fundamental voltage (V) at different modulation indices

| Modulation | Fundamental Voltage (V) |                  |

|------------|-------------------------|------------------|

| Index      | Analytical Value        | Simulation Value |

| 0.265      | 20.24                   | 20.13            |

| 0.340      | 25.97                   | 26.04            |

| 0.444      | 33.92                   | 34.21            |

| 0.537      | 41.02                   | 41.00            |

| 0.682      | 52.10                   | 52.10            |

| 0.787      | 60.12                   | 60.13            |

| 0.853      | 65.16                   | 65.10            |

| 0.912      | 69.67                   | 69.66            |

Presented in Table II is the comparative analysis of the analytical and simulation values of the 49<sup>th</sup> order THD at different modulation indices.

TABLE II: Analytical and simulation values of THD (%) at different modulation indices

| Modulation | THD (%)          |                  |

|------------|------------------|------------------|

| Index      | Analytical Value | Simulation Value |

| 0.265      | 21.53            | 19.93            |

| 0.340      | 12.46            | 11.08            |

| 0.444      | 9.25             | 7.98             |

| 0.537      | 7.99             | 6.37             |

| 0.682      | 6.29             | 5.67             |

| 0.787      | 6.01             | 4.95             |

| 0.853      | 5.21             | 4.36             |

| 0.912      | 4.66             | 3.48             |

It can be seen from the tables that the simulation values closely agree with the analytical values. It should be noted that THD values of 52.54%, 23.14%, and 15.47% are

shown in Figures 7, 8, and 9, respectively; the reason for this is that the THD values shown are for phase voltages which include triplen harmonic components while analytical values are for line voltages which exclude triplen harmonic components.

Practical implementation of the proposed method requires a low pass filter at the output of the inverter to attenuate higher order harmonics. This will ensure that THD in the output voltage of the inverter satisfy THD limit of 5% specified by IEEE-519 standard for complete working range of modulation indices. There are two approaches to the real-time implementation of the proposed method. In the first approach, values of the switching angles for different modulation indices calculated offline with RCGA are stored in look-up tables of a microprocessor-based modulator. This approach requires a large memory. In the second approach, the results of RCGA are used to train a pattern recognition algorithm such as Artificial Neural Network (ANN), and a high-speed digital signal processor is used to generate the appropriate switching angles for each modulation index in real time. Computation of the switching angles in real time is, as at present, impossible.

### VI. CONCLUSION

The transcendental nonlinear equations that characterize the fundamental as well as 5<sup>th</sup>, 7<sup>th</sup>, 11<sup>th</sup> and 13<sup>th</sup> harmonics in an 11-level inverter have been solved with RCGA implemented with MATLAB software. It is observed that RCGA is globally convergent and highly successful for low order harmonic reduction. The fundamental voltage is obtained at desired values while the selected low order harmonics are well attenuated as their values tend towards zero. Analytically observed results are validated with simulations at different modulation indices, and both are in close agreement. It has been shown that drives application requirements of a wide range of modulation index and significant amount of THD reduction can be attained by computing all possible solutions.

#### VII. REFERENCES

- S. Bell and J. Sung," Will Your Motor Insulation Survive a New Adjustable Frequency Drive?," IEEE Transactions on Industry Application, Volume 33, Sept. 1997, pp. 1307-1311.

- [2] R. H. Baker and L. H. Bannister, "Electric power converter," U.S. Patent 3867643, Feb. 1975.

- [3] J. Rodríguez, J. Lai, F.Peng, "Multilevel inverters: a survey of topologies, controls and applications," *IEEE Transactions on Industry Applications*, vol. 49, no. 4, Aug. 2002, pp. 724-738.

- [4] S. Khomfoi, L. M Tolbert, Chapter31.Multilevel PowerConverters.The University of Tennessee.pp.31-1 to 31-50.

- [5] A. Nabae, I. Takahashi and H. Akagi, "A new neutralpoint clamped PWM inverter,"*IEEE Trans. Ind. Applicat.*, vol. IA-17, Sept./Oct. 1981, pp. 518–523.

- [6] T. A. Meynard and H. Foch, "Multi-level conversion: High voltage choppers and voltage- source inverters," in *Proc. IEEE-PESC*, 1992, pp. 397–403.

- [7] P. Hammond, "A new approach to enhance power quality for medium voltage ac drives," *IEEE Trans. Ind. Applicat.*, vol. 33, pp. 202–208, Jan./Feb. 1997

- [8] A. K. Al-Othman, N. A. Ahmed, A. M. Al-Kandari and H. K. Ebraheem, "Selective Harmonic Elimination of PWM AC/AC Voltage Controller Using Hybrid RGA-PS Approach," in Proceedings of World Academy of Science and Technology Volume 23, Aug. 2007, pp. 140-146.

- [9] J. Kumar, B. Das, and P. Agarwal, "Selective Harmonic Elimination Technique for Multilevel Inverter," 15<sup>th</sup> National Power System Conference (NPSC), IIT Bombay, 2008, pp. 608-613.

- [10] J. N. Chiasson, L. M. Tolbert, K. J. McKenzie, and Z. Du, "Control of a Multilevel Converter Using Resultant Theory," IEEE Transaction on Control Systems Technology, vol. 11, no. 3, May 2003, pp. 345-353.

- [11] F. Swift and A. Kamberis, "A New Walsh Domain Technique of Harmonic Elimination and Voltage Control In Pulse-Width Modulated Inverters," IEEE Transactions on Power Electronics, volume 8, no. 2, 1993, pp. 170–185.

- [12] T. J. Liang and R. G. Hoft, "Walsh Function Method of Harmonic Elimination," Proceedings of IEEE Appl. Power Electron. Conference, 1993, pp.847– 853.

- [13] T. J. Liang, R. M. O'Connell, R. M. and R. G. Hoft, "Inverter Harmonic Reduction Using Walsh Function Harmonic Elimination Method," IEEE Transaction on Power Electron, volume 12, no. 6, 1997, pp. 971– 982.

- [14] B. Ozpineci, L. M. Tolbert, and J. N. Chiasson, "Harmonic Optimization of Multilevel Converters Using Genetic Algorithm," 35 Annual IEEE Power Electronics Specialists Conference, Germany, 2004.

- [15] R. Salehi, N. Farokhia, M.Abedi, and S.H. Fathi, "Elimination of Low Order Harmonics in Multilevel Inverters Using Genetic Algorithm," Journal of Power Electronics, volume 11, no. 2, Mar. 2011, pp. 132-139.

- [16] K. Sundareswaran, K. Jayant, and T. N. Shanavas, "Inverter Harmonic Elimination through a Colony of Continuously Exploring Ants," IEEETransactions on

Industrial Electronics, volume 54, no. 5, 2007, pp. 2558-2565.

- [17] A. Kavousi, et. al., "Application of the Bee Algorithm for Selective Harmonic Elimination Strategy in Multilevel Inverters," IEEE Transaction on Power Electronics, vol. 27, no. 4, pp.1689-1696, April 2012.

- [18] N. Vinoth, and H. Umeshprabhu, "Simulation of Particle Swarm Optimization Based Selective Harmonic Elimination,"International Journal of Engineering and Innovative Technology (IJEIT) Volume 2, Issue 7, 2013, pp. 215-218.

- [19] J. H. Holland, Adaptation in Natural and Artificial Systems (U. Michigan Press, Ann Arbor, Mich., 1975).

- [20] T. Srikanth and V. Kamala,"A Real Coded Genetic Algorithm for Optimization of Cutting Parameters in Turning," International Journal of Computer Science and Network Security, vol. 8, no. 6, June 2008, pp.189-193

- [21] R. Salehi, N. Farokhia, M. Abedi, and S.H. Fathi, "Elimination of Low Order Harmonics in Multilevel Inverters Using Genetic Algorithm," Journal of Power Electronics, volume 11, no. 2, Mar. 2011, pp. 132-139.